# 基于 FPGA 的 IRIG-B 码产生器设计与实现

冯胜民 陈娟花 王国林 陈思兵

(63726 部队 银川 750004)

摘 要:随着大规模集成电路和可编程技术的发展,对靶场时统设备的可编程度、集成度的要求越来越高,特别是对于车载测控设备,由于受空间、运输等条件的限制,对时统设备的体积、可靠性提出了更高的要求。结合靶场时统研究项目,提出了一种基于 FPGA 的 IRIG-B 码产生器的设计方案,以 Cyclone IV FPGA 芯片 EP4CE22 为核心,采用原理图和 Verilog语言进行编程实现。它具有操作简单、可靠性高、功能拓展性强、体积小等优点,可广泛应用于靶场测控设备之中。

关键词:时统设备; FPGA; B码产生器; 设计与实现

中图分类号: V556.6 文献标识码: A 国家标准学科分类代码: 590.6020

# Design and implication of IRIG-B code generator based on FPGA

Feng Shengmin Chen Juanhua Wang Guolin Chen Sibing

(PLA Unit 63726, Yinchuan 750004, China)

Abstract: With the development of large-scale integrated circuit and programmable technique, the degree of integration and programmable ability for timing equipment have been required higher and higher in the test range. As the restriction of space and transportation condition, it puts forward higher requirements for the volume and reliability of timing equipment especially for the vehicle equipment. Combining with the research project of test range timing equipment, a design project of IRIG-B code generator is proposed based on FPGA by the Cyclone IV FPGA chip EP4CE22 as the core and schematic diagram and Verilog language programming. The system has the characters of simple operation, high reliability, smaller volume and strong function expansion, which can widely be applied to measurement and control equipment of test range,

Keywords: timing equipment; FPGA; B code generator; design and implication

#### 1 引 言

在航天武器试验靶场中,时间统一设备主要为各测控设备提供标准的时间信息和频率基准,协同各测量设备同步工作[1]。

目前,靶场时统设备通常采用分离元件和小规模集成电路设计,结构复杂,集成度低,另外由于技术保密等原因,外购的时统设备核心内容不能掌握,导致对设备的维护、保养、维修性差<sup>[2-3]</sup>。随着大规模集成电路和可编程技术的发展,对靶场时统设备的可编程度、集成度的要求越来越高,特别是对于车载测控设备,由于受空间、运输等条件的限制,对时统设备的体积、可靠性等提出了更高的要求<sup>[4-7]</sup>。

针对以上问题和需求,结合靶场时统设备研究项目,提出了一种基于 FPGA<sup>[8-9]</sup>的靶场时统板设计方案,它以Altera 公司的 Cyclone IV FPGA 芯片 EP4CE22 为核心<sup>[10]</sup>,采用原理图和 Verilog 语言<sup>[11]</sup>混合编程,通过接收 GPS、北

斗、外B码等外部基准,选择其中一路产生与其同步的IRIG-B码信号和各脉冲信号,供其他分系统使用。该时统板由于基于FPGA设计实现,具有软件无线电所具有的灵活性、开放性等特点,且可靠性大幅提高,抗干扰性能大大增强,最重要的是由于能结合实际应用需求,技术资料完善,使分机操作人员对系统的掌控能力、维护保养维修能力有了极大地提高。

# 2 IRIG-B 码的编码方法

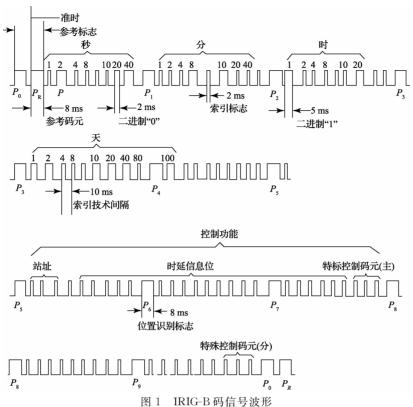

IRIG-B格式时间码(简称 B码)为国际通用时间格式码,用于各系统的时间同步,IRIG-B码信号波形图见图 1 所示。

B码每秒发出一帧时间串码,每个码元宽度为 10 ms,一个时帧周期包括 100 个码元,为脉宽编码。码元的"准时"参考点是其脉冲前沿,时帧的参考标志由一个位置识别标志和相邻的参考码元组成,其宽度为 8 ms;每 10 个码元有一个位置

识别标志:  $P_1$ ,  $P_2$ ,  $P_3$ ,  $\cdots$ ,  $P_9$ ,  $P_0$ , 它们均为 8 ms 宽度; PR 为帧 参考点; 二进制"1"和"0"的脉宽为 5 ms 和 2 ms。

1个时间格式帧从帧参考标志开始,连续 2 个 8 ms 宽脉冲表明秒的开始,如果从第 2 个 8 ms 开始对码元进行编码,分别为第 0,1,2,…,99 个码元。在 B 码时间格式中含有天、时、分、秒。时序为秒、分、时、天,所占信息位为秒 7 位、分 7 位、时 6 位、天 10 位,其位置在  $P_1 \sim P_5$ 。  $P_6 \sim P_0$  包含其他控制信息。其中"秒"信息为第 1,2,3,4,6,7,8 码元;"分"信息为第 10,11,12,13,15,16,17 码元;"时"信息为第 20,21,22,23,25,26,27 码元;第 5,14,24 码元为索引标志,宽度为 2 ms。时、分、秒均用 BCD 码表示,低位在

前,高位在后;个位在前,十位在后。

# 3 硬件设计方案

## 3.1 系统原理及组成

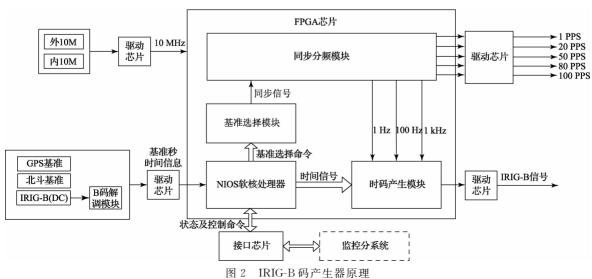

系统主要由 GPS/北斗接收模块、外部 B 码接收解调模块、FPGA 电路、接口驱动电路、10 M 时钟电路等组成。在 FPGA 中又设计了 NIOS 软核处理器模块、基准选择模块、同步分频模块、时码产生模块 4 个软模块。基于 FPGA设计的 IRIG-B 码产生器原理如图 2 所示。

GPS/北斗 OEM 板输出的秒信号和串行时间数据、外 部 IRIG-B(DC)信号经单片机解调输出的秒信号和串行时 间数据,经驱动接口芯片送送 FPGA 中,NIOS 软核处理器 对串行时间数据进行接收、变换并保存在指定的缓冲区 中,并对所有外部基准进行判别,根据基准状态及监控信 息,向基准选择模块送基准选择命令,基准选择模块为同 步分频模块提供时间基准信号 1 PPS。同步分频模块接收 外部或本地晶振提供的 10 MHz 信号,进行分频和同步后 产生其他设备所需要的 1 PPS、20 PPS、50 PPS 同步脉冲 信号,还可对同步误差进行测量、监视、比较,当同步误差 大于 0,4 us 时自动进行同步,确保时间同步误差在规定的 误差范围内。时码产生模块接收同步分频模块提供的1 Hz、100 Hz、1 kHz 信号和 NIOS 软核处理器输出的 BCD 格式的时间数据,采用原理图与 Verilog 语言混合编程,通 过设计一个百进制计数器对 100 PPS 信号进行计数,基准 秒信号进行清零,在 Verilog 中利用 Switch 语句,根据计数 结果选择使能是8 ms、5 ms、2 ms 脉宽电平信号,最后3 路 信号进行"或"运算,即可得到产生的 B 码信号,经接口芯 片输出。

同时 FPGA 中的 NIOS 软核处理器通过异步串口将时、分、秒数据、位置信息等发送给监控软件,接收监控软件下发的控制命令。

#### 3.2 单元模块设计

#### 1)FPGA 电路模块

作为 IRIG-B 码产生器的核心, FPGA 电路模块主要实现了 NIOS 软核处理器、同步分频、时码产生、基准选择等功能。

在硬件设计中,FPGA 芯片选用 Altera 公司 Cyclone IV 系列 EP4CE22E22I7,它具有 22 323 个逻辑单元、594 Kbits的嵌入式存储器、 $66 \land 18 \times 18$  嵌入式乘法器、4个通用的 PLL、8 个 I/O 块,最大用户 I/O 为  $153 \land$ ,完全可以满足设计的需要。

FPGA 芯片的 I/O 供电电压为 3.3 V,内核电压为 1.2 V,PLL 供电电压为 2.5 V,采用集成低压降三端线性 稳压器 LM1117 芯片供电。

由于 Cyclone IV 器件使用 SRAM 单元存储配置数据,每次器件上电后,配置数据会被下载 FPGA 芯片中,根据 FPGA 的配置数据大小,选用低成本的 Altera EPCS 系列串行闪存器件 EPCS16 进行数据配置。

#### 2)GPS/北斗接收模块

GPS/北斗接收模块选用长沙天穹电子科技有限公司的 EZ3204 北斗授时模块,通过加装 Ublox-5T GPS 授时模块后即自动成为双模授时模块。它具有接收 GPS L1 点频、北斗 B1 点频所有卫星信号的能力,可工作在单独 GPS 模式、北斗模式,也可工作在 GPS 北斗兼容模式。当模块工作在单独的 GPS 模式和北斗模式时,其输出地 GPS 秒、北斗秒的通过接收 GPS、北斗信号,可输出 GPS 秒、北斗

秒,授时精度为 30ns 左右,输出的串行时间数据格式可通过软件进行配置。

在本设计中,GPS 和北斗串行数据均采用 RMC 格式,每秒 1 帧,内容包括:UTC 时间、经纬度、日期、数据状态等,可满足设计要求。

#### 3)外部 B 码接收解调模块

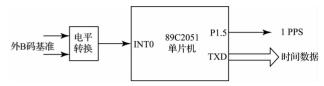

当采用外部 B 码信号作为产生 IRIG-B 码的基准时,需要对外部 B 码基准进行接收解调,以产生基准秒和串行时间数据。在本设计中,采用 89C2051 单片机完成对外部 B 码基准的解调工作,原理如图 3 所示。

图 3 外部 B 码基准解码原理

外部 B 码基准信号经电平转换后,将 RS422 电平转换为 TTL 电平,送单片机的外部中断 0 引脚,与定时器 0 一起完成对每个码元宽度的测量,根据两个连续的 8 ms 码元找到帧头,然后通过对码元计数,分别解调出秒信号和时间数据。秒信号通过单片机的 P1.5 引脚送出,时间数据通过单片机的串行口发送。

# 4)接口驱动电路模块

接口驱动电路模块主要完成与 FPGA 的外部数据通信。由于 FPGA 的 I/O 口接口电平为 LVCOM 电平,支持的电压为 3.3 V,所以当外部信号输入 FPGA 或从 FPGA 输出时,必须进行电平变换,另外还可起到保护 FPGA 芯片的目的。

接口芯片选用 SN74LVTH245APW,其输入信号电压 最大可达 7 V,输出电压为 3.3 V,与 FPGA 的 I/O 兼容。

#### 5)10 M 时钟电路模块

10 M 信号主要用于同步分频,通过同步分频,产生需要的各种同步脉冲信号。本方案设计支持内部 10 M 和外部 10 M 信号输入。

内部 10M 信号的产生选用恒温晶振 OX36D-H-MR-V @ 10M,输出 10M 信号的准确度可达 10<sup>-8</sup> 左右。

#### 4 软件设计

软件设计主要包括两部分内容:一是用于解调外部B码基准的单片机软件,采用汇编语言编写,使用WAV6000软件进行开发;二是用于同步分频、基准选择、时码产生、数据通信的FPGA软件,采用原理图和Verilog编写,使用Quartus II 10.0软件开发,下面主要对软件设计进行阐述。

#### 4.1 外 B 码基准解调模块

外 B 码基准解调模块软件主要完成对 B 码的解调,通

过 P1.5 引脚输出基准秒信号,通过单片机串口输出时间数据。软件模块主要包括主程序、测量码元宽度中断服务程序、串行数据发送程序、搜索帧头子程序、码元计数子程序、译码子程序等。

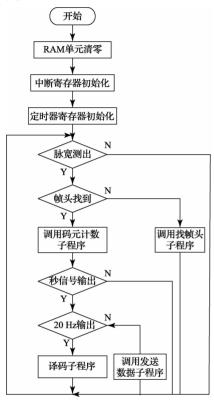

主程序主要完成单片机 RAM 单元清零、中断寄存器、定时器寄存器等初始化工作,初始化完成后,程序进入死循环,等待中断产生,执行串行数据发送程序、搜索帧头子程序、码元计数子程序、译码子程序等。主程序的流程图见图 4 所示。

图 4 外 B 码基准解调主程序流程

测量码元宽度中断服务程序采用单片机外部中断 0 和定时器 0 协同工作,在 B 码码元的上升沿,定时器开始 计数,在下降沿定时器停止计数,外部中断 0 产生中断,在 中断服务程序中将定时器中的计数值读出,即为测量出的 码元宽度。

搜索帧头子程序主要是找 B 码信号的帧头, 当测量出的连续 2 个码元宽度为 8 ms 时, 即表示找到帧头, 设置码元计数变量。

码元计数子程序主要完成对 B 码码元中的位置识别标志和该位置下的码元进行计数,位置识别标志采用 40H 变量进行计数,该位置识别区的码元采用 41H 变量进行计数,主要为后续译码子程序使用。

译码子程序根据 40H、41H 2 个变量的值,分别检测 B 码码元中的时、分、秒等数据,并保存在时间数据缓冲区中。

串行数据发送子程序主要对保存在时间数据缓冲区中的数据通过单片机串口进行发送,波特率为 19 200 bps, 帧速率为 20 fps,数据包括帧头、十六进制的时分秒数据、秒的 20 Hz 计数值、校验、帧尾等。单片机串口工作在方式一,即为 8 位的 UART 数据通信。

#### 4.2 FPGA 软件模块

在 FPGA 软件中设计了 NIOS 软核处理器、同步分频模块、基准选择模块、时码产生模块 4 部分。下面对各模块设计进行详细介绍。

## 1)NIOS 软核处理器模块

利用 Quartus 软件中 SOPC 开发工具,设计开发了 NIOS 软核处理器模块,在模块中设计了 5 个串口用于接收 GPS、北斗、外 B 码数据,向监控分系统发送测量数据、上报状态,并接收基准选择命令。

在模块中还设计了 PIO 单元,主要完成向时码产生模块发送 BCD 格式的时间数据,向基准选择模块发送基准选择命令,接收 GPS、北斗、外 B 码的秒信号,以进行各个基准状态的判断。

#### 2) 同步分频模块

同步分频模块主要对输入的  $10\,M$  信号进行分频。分频器采用二-五-十进行制计数器  $7490\,$ 完成,分频出  $1\,MHz$ 、 $100\,kHz$ 、 $10\,kHz$ 、 $2\,kHz$ 、 $1\,kHz$ 、 $400\,$  PPS、 $100\,$  PPS、 $80\,$  PPS、 $50\,$  PPS、 $20\,$  PPS、 $2\,$  PPS、 $1\,$  PPS 等信号,并且对分频的  $1\,$  PPS 与同步秒信号进行比对,当误差大于  $0.4\,$   $\mu$ s 时,对分频链进行同步,使输出的各同步脉冲信号与基准秒信号相位误差满足指标要求。

#### 3)基准选择模块

基准选择模块根据下发的基准选择命令从 GPS、北 斗、外 B 码 3 个基准中选择一路,作为时码产生和同步分 频的基准,在模块中主要利用多路数据选择器实现。

#### 4)时码产生模块

时码产生模块主要采用原理图和 Verilog 语言混合编程实现。在时码产生模块中,设计了一个百进制计数器,对分频模块输出的 100PPS 进行计数,计数范围为 0~99, 当基准秒到来时,对计数器进行清零。

采用 Verilog 语言编程实现时码信号的产生,原理为: 读取计数器的计数值,当为 0、9、19、…、99 时,输出 8 ms 信号;当为 1、2、3、4、6、7、8 时,分别根据当前秒的 BCD 数据判断,当为 0 时输出 2 ms 信号,当为 1 时输出 5 ms 信号;以此类推,分别对分、时等数据进行编码。最后对输出地 8 ms信号、5 ms 信号、2 ms 信号进行"或"运算,即产生输出 B 码信号。

# 5 实验结果

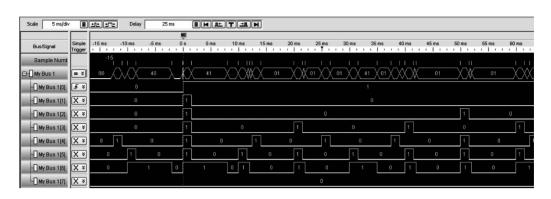

采用逻辑分析仪对 B 码产生器的各输出信号进行了测试,在测试中,选用 GPS 基准秒的上升沿进行触发,接探头的 My Bus[0],输出的同步脉冲信号 1PPS 接探头的 My

Bus[1],20PPS 信号接探头的 My Bus[2],50PPS 信号接探头的 My Bus[3],80PPS 信号接探头的 My Bus[4],100PPS 信号接探头的 My Bus[5],输出的 B 码信号接探

头的 My Bus[6]。对电路板加电,选择 GPS 基准,输出的 1PPS、20PPS、50PPS、80PPS、100PPS 同步信号和 B 码信号波形如图 5 所示。

图 5 输出的同步信号和 B 码信号波形

从上图来看,在选用 GPS 作为基准时,输出的各同步脉冲信号和产生的 B 码信号的准时参考点(连续 2 个 8 ms 码元的第二个码元前沿)与 GPS 秒的前沿同步,经测定同步误差小于 0.4 us,满足设计要求。

# 6 结 论

目前,该时统板已成功应用于某光测设备之中,经过长时间工作检验,设备工作稳定,指标满足要求。在时统板的设计中,由于采用了Altera公司的飓风四代FPGA芯片EP4CE22E22I7进行设计和系统构建,将新一代FPGA芯片应用于靶场时统板的设计之中,使得时统板不仅满足了基本任务需求,而且使得系统的灵活性、功能拓展性、可靠性等均有明显的提升。

# 参考文献

- [1] 刘明波,耿文建,华安,等. IRIG-B 码的产生与解调系统设计与实现[J]. 国外电子测量技术,2010,29(5): 47-51.

- [2] 吴卫,陈建军,宋虎.基于 FPGA 的 IRIG-B 码解码器 的实现[J]. 雷达与对抗,2009(3):37-40.

- [3] 朱伟. 嵌入式电子校准技术在天馈线测试仪中的应用[J]. 国外电子测量技术,2014,33(4):15-17.

- [4] 冯胜民,赵春晖,梁彦,等. 基于 ISA 总线的 B 码终端 卡设计与实现[J]. 测控技术,2012,31(3);36-39.

- [5] 王鹏,程芸,董书莉.基于 FPGA 的多格式数据传输设计[J]. 电子测量技术,2014,37(1):70-75.

- [6] 黄赛帅. 靶场时统设计[D]. 南京: 南京理工大学,2009.

- [7] 卢祥弘. GPS 同步校频技术在三维电磁采集系统中的应用「D」、长沙:中南大学,2010.

- [8] 吴丛中,彭乐,王亚君,等. USB3.0 设备控制器 IP 核 OUT 端点测试平台的研究与实现[J]. 电子测量与仪 器学报,2012,26(7):646-651.

- [9] 陈曦,杨亮,李鹏斐,等. 基于 FPGA 的静电[J]. 仪器 仪表学报,2013,34(8):1901-1906.

- [10] 吴厚航. 深入浅出玩转 FPGA[J]. 北京: 北京航空航天大学出版社, 2010.

- [11] 刘靳,刘笃仁. Verilog 程序设计与 EDA[M]. 西安:西安电子科技大学出版社,2012.

#### 作者简介

**冯胜民**,工学硕士,工程师。主要研究方向为雷达测控、嵌入式系统开发等。

E-mail: fsmfkx11@163.com